# Filter Design HDL Coder

For Use with MATLAB®

- Computation

- Visualization

- Programming

Version 1

#### How to Contact The MathWorks:

Web www.mathworks.com

comp.soft-sys.matlab Newsgroup

Technical Support support@mathworks.com

Product enhancement suggestions suggest@mathworks.com Bug reports bugs@mathworks.com

Documentation error reports doc@mathworks.com

Order status, license renewals, passcodes service@mathworks.com Sales, pricing, and general information info@mathworks.com

508-647-7000 Phone

508-647-7001 Fax

The MathWorks, Inc. 3 Apple Hill Drive

Natick, MA 01760-2098

For contact information about worldwide offices, see the MathWorks Web site.

Mail

Filter Design HDL Coder User's Guide © COPYRIGHT 2004 by The MathWorks, Inc.

The software described in this document is furnished under a license agreement. The software may be used or copied only under the terms of the license agreement. No part of this manual may be photocopied or reproduced in any form without prior written consent from The MathWorks, Inc.

FEDERAL ACQUISITION: This provision applies to all acquisitions of the Program and Documentation by, for, or through the federal government of the United States. By accepting delivery of the Program or Documentation, the government hereby agrees that this software or documentation qualifies as commercial computer software or commercial computer software documentation as such terms are used or defined in FAR 12.212, DFARS Part 227.72, and DFARS 252.227-7014. Accordingly, the terms and conditions of this Agreement and only those rights specified in this Agreement, shall pertain to and govern the use, modification, reproduction, release, performance, display, and disclosure of the Program and Documentation by the federal government (or other entity acquiring for or through the federal government) and shall supersede any conflicting contractual terms or conditions. If this License fails to meet the government's needs or is inconsistent in any respect with federal procurement law, the government agrees to return the Program and Documentation, unused, to The MathWorks, Inc.

MATLAB, Simulink, Stateflow, Handle Graphics, and Real-Time Workshop are registered trademarks, and TargetBox is a trademark of The MathWorks, Inc.

Other product or brand names are trademarks or registered trademarks of their respective holders.

Printing History:

June 2004 Online only New for Version 1.0 (Release 14)

# **Contents**

## **Getting Started**

| 1 | What Is the Filter Design HDL Coder?                 |

|---|------------------------------------------------------|

| , | Expected Users                                       |

|   | Key Features and Components                          |

|   | FDATool Plug-In — the GUI                            |

|   | Command-Line Interface                               |

|   | Quantized Filters — the Input                        |

|   | Filter Properties — Input Parameters                 |

|   | Generated HDL Files — the Output                     |

| 1 | nstallation                                          |

| _ | Checking Product Requirements                        |

|   | Installing the Software                              |

| ( | Getting Help with the Filter Design HDL Coder        |

|   | Coder                                                |

|   | Online Help                                          |

|   | Using "What's This?" Context-Sensitive Help          |

|   | Demos and Tutorials                                  |

| ŀ | Applying the Filter Design HDL Coder to the Hardware |

|   | Design Process                                       |

|   | Tutorials — Generating HDL Code for File             |

| _ |                                                      |

| ( | Creating a Directory for Your Tutorial Files         |

|   |                                                      |

| •   | Overview of Generating HDL Code for a Filter Design                      |

|-----|--------------------------------------------------------------------------|

| )   | Design 3-3                                                               |

|     |                                                                          |

| • [ | Generating HDL Code for a Filter Design                                  |

|     |                                                                          |

|     | Code                                                                     |

|     | Code                                                                     |

|     | Code                                                                     |

|     | Quantizing the IIR Filter                                                |

|     | IIR Filter Tutorial2-43Designing an IIR Filter2-43                       |

|     | Verifying the FIR Filter's Optimized Generated Verilog Code              |

|     | Getting Familiar with the FIR Filter's Optimized Generated  Verilog Code |

|     | Configuring and Generating the FIR Filter's Optimized Verilog  Code      |

|     | Designing the FIR Filter 2-23 Quantizing the FIR Filter 2-25             |

|     | Optimized FIR Filter Tutorial                                            |

|     | Code 2-16                                                                |

|     | Code                                                                     |

|     | Code                                                                     |

|     |                                                                          |

| Default Settings for General HDL Code                                                  | 3-10 |

|----------------------------------------------------------------------------------------|------|

| Default Settings for Code Optimizations                                                | 3-11 |

| Default Settings for Test Benches                                                      | 3-12 |

| What Are Your HDL Requirements?                                                        | 3-13 |

| Setting the Target Language                                                            | 3-18 |

| Setting the Names and Location for Generated HDL                                       |      |

| Files                                                                                  | 3-19 |

| Setting Filter Entity and General File Naming                                          |      |

| Strings                                                                                |      |

| Redirecting Filter Design HDL Coder Output Setting the Postfix String for VHDL Package |      |

| Files                                                                                  | 3-22 |

| Splitting Entity and Architecture Code into Separate                                   | 0.00 |

| Files                                                                                  | 3-23 |

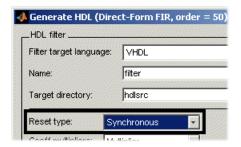

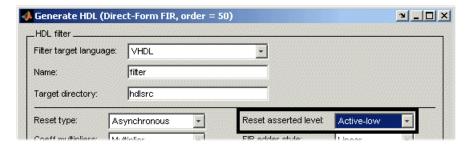

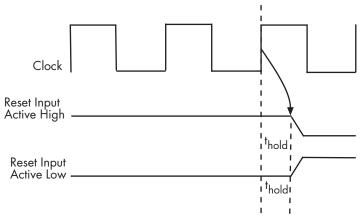

| Customizing Reset Specifications                                                       | 3-26 |

| Setting the Reset Style for Registers                                                  | 3-26 |

| Setting the Asserted Level for the Reset Input                                         |      |

| Signal                                                                                 | 3-28 |

| Customizing the HDL Code                                                               | 3-29 |

| Specifying a Header Comment                                                            |      |

| Specifying a Prefix for Filter Coefficients                                            |      |

| Setting the Postfix String for Resolving Entity or Module Nat                          |      |

| Conflicts                                                                              |      |

| Setting the Postfix String for Resolving HDL Reserved Word                             |      |

| Conflicts                                                                              | 3-34 |

| Setting the Postfix String for Process Block                                           |      |

| Labels                                                                                 | 3-37 |

| Naming HDL Ports                                                                       | 3-38 |

| Specifying the HDL Data Type for Data Ports                                            | 3-40 |

| Suppressing Extra Input and Output Registers                                           | 3-42 |

| Minimizing Quantization Noise for Fixed-Point                                          |      |

| Filters                                                                                | 3-43 |

| Representing Constants with Aggregates                                                 |      |

| Unrolling and Removing VHDL Loops                                                      |      |

| Using the VHDL rising_edge Function                                                    |      |

| Suppressing the Generation of VHDL Inline                                              |      |

| Configurations                                                                         | 3-48 |

|   | Specifying VHDL Syntax for Concatenated                                                        | 0.40         |

|---|------------------------------------------------------------------------------------------------|--------------|

|   | Zeros Summagain a Vanilan Tima Scala Directives                                                |              |

|   | Suppressing Verilog Time Scale Directives<br>Suppressing the Initialization of Signals of Type | 3-90         |

|   | REAL                                                                                           | 3-51         |

|   | Specifying Input Type Treatment for Addition and Subtraction                                   |              |

|   | Operations                                                                                     |              |

|   | •                                                                                              |              |

|   | Setting Optimizations                                                                          |              |

|   | Optimizing Generated Code for HDL                                                              |              |

|   | Optimizing Coefficient Multipliers                                                             |              |

|   | Optimizing Final Summation for FIR Filters                                                     | 3-57         |

|   | Optimizing the Clock Rate with Pipeline                                                        | - <b>-</b> - |

|   | Registers                                                                                      |              |

|   | Setting Optimizations for Synthesis                                                            | 3-59         |

|   | Customizing the Test Bench                                                                     | 3-61         |

|   | Renaming the Test Bench                                                                        |              |

|   | Specifying a Test Bench Type                                                                   |              |

|   | Configuring the Clock                                                                          |              |

|   | Configuring Resets                                                                             |              |

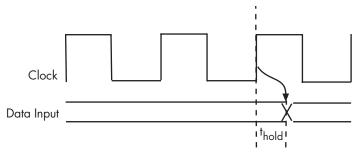

|   | Setting a Hold Time for Data Input Signals                                                     |              |

|   | Setting an Error Margin for Optimized Filter                                                   |              |

|   | Code                                                                                           | 3-70         |

|   | Setting Test Bench Stimuli                                                                     |              |

|   |                                                                                                |              |

|   | Generating the HDL Code                                                                        | 3-74         |

|   |                                                                                                |              |

|   | Testing a Filter Des                                                                           | ign          |

| 4 |                                                                                                |              |

| • | Overview of the Test Methods                                                                   | 4-2          |

|   |                                                                                                |              |

|   | Testing with an HDL Test Bench                                                                 | 4-3          |

|   | Generating the Filter and Test Bench HDL Code                                                  |              |

|   | Starting the Simulator                                                                         | 4-7          |

|   | Compiling the Generated Filter and Test Bench                                                  |              |

|   | Files                                                                                          |              |

|   | Running the Test Bench Simulation                                                              | 4-8          |

|   | Testing with a ModelSim Tcl/Tk DO File       | 4-12       |

|---|----------------------------------------------|------------|

|   | File Starting ModelSim                       | 4-15       |

|   | Compiling the Generated Filter File          |            |

|   |                                              |            |

|   | Properties — Categorical L                   | ist        |

| 5 |                                              |            |

|   | Language Selection Properties                | 5-2        |

|   | File Naming and Location Properties          | 5-2        |

|   | Reset Properties                             | <b>5-2</b> |

|   | Header Comment and General Naming Properties | 5-3        |

|   | Port Properties                              | <b>5-4</b> |

|   | Advanced Coding Properties                   | 5-4        |

|   | Optimization Properties                      | 5-6        |

|   | Test Bench Properties                        | 5-6        |

| 6          | Properties — Alphabetical List    |

|------------|-----------------------------------|

| <b>7</b>   | Functions — Alphabetical List     |

| Λ 1        | Examples                          |

| <b>A</b> I | Tutorials A-2                     |

|            | Basic FIR Filter Tutorial A-3     |

|            | Optimized FIR Filter Tutorial A-4 |

|            | IIR Filter Tutorial               |

Index

# Getting Started

This chapter introduces you to the Filter Design HDL Coder by discussing the following topics:

"What Is the Filter Design HDL Coder?" (p. 1-2)

"Installation" (p. 1-9)

"Getting Help with the Filter Design HDL Coder" (p. 1-10)

"Applying the Filter Design HDL Coder to the Hardware Design Process" (p. 1-13)

Describes key product features and

components

Explains how to install and set up the Filter Design HDL Coder

Discusses ways of applying the Filter Design HDL Coder to the hardware design process, including signal analysis, algorithm verification, and reference design validation

Identifies and explains how to gain access to available documentation and online help resources

### What Is the Filter Design HDL Coder?

The Filter Design HDL Coder accelerates the development of application-specific integrated circuit (ASIC) and field programmable gate array (FPGA) designs and bridges the gap between system-level design and hardware development by generating hardware description language (HDL) code based on filters developed in MATLAB®. Currently, system designers and hardware developers use HDLs, such as very high speed integrated circuit (VHSIC) hardware definition language (VHDL) and Verilog, to develop hardware designs. Although HDLs provide a proven method for hardware design, the task of coding filter designs, and hardware designs in general, is labor intensive and the use of these languages for algorithm and system-level design is not optimal.

Using the Filter Design HDL Coder, system architects and designers can spend more time on fine-tuning algorithms and models through rapid prototyping and experimentation and less time on HDL coding. Architects and designers can efficiently design, analyze, simulate, and transfer system designs to hardware developers.

In a typical use scenario, an architect or designer uses the Filter Design Toolbox, its Filter Design and Analysis Tool (FDATool), and the Filter Design HDL Coder to design a filter. Then, with the click of a button, the Filter Design HDL Coder generates a VHDL or Verilog implementation of the design and a corresponding test bench. The generated code adheres to a clean HDL coding style that enables architects and designers to quickly address customizations, as needed. The test bench feature increases confidence in the correctness of the generated code and saves potential time spent on test bench implementation.

#### The following sections discuss

- "Expected Users" on page 1-3

- "Key Features and Components" on page 1-3

- "FDATool Plug-In the GUI" on page 1-4

- "Command-Line Interface" on page 1-5

- "Quantized Filters the Input" on page 1-6

- "Filter Properties Input Parameters" on page 1-7

- "Generated HDL Files the Output" on page 1-8

#### **Expected Users**

Filter Design HDL Coder users are system and hardware architects and designers who develop, optimize, and verify hardware signal filters. These designers are experienced with VHDL or Verilog, but can benefit greatly from a tool that automates HDL code generation. The Filter Design HDL Coder interface provides designers with efficient means for creating test signals and test benches that verify algorithms, validating models against standard reference designs, and translate legacy HDL descriptions into system-level views.

Users are also expected to have prerequisite knowledge in the following subject areas:

- Hardware design and system integration

- VHDL or Verilog

- MATLAB

- Filter Design Toolbox

- HDL simulators, such as ModelSim<sup>®</sup>

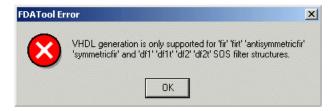

#### **Key Features and Components**

Key features and components of Filter Design HDL Coder include

- Graphical user interface (GUI) plug-in to the Filter Design and Analysis Tool (FDATool)

- MATLAB command line interface

- Support for the following filter structures:

- Finite impulse response (FIR)

- Antisymmetric FIR

- Transposed FIR

- Symmetric FIR

- Second-order section (SOS) infinite impulse response (IIR) Direct Form I

- SOS IIR Direct Form I transposed

- SOS IIR Direct Form II

- SOS IIR Direct Form II transposed

- Generation of code that adheres to a clean HDL coding style

- Options for optimizing numeric results of generated HDL code

- Options for controlling the contents and style of the generated HDL code and test bench

- Test bench generation for validating the generated HDL filter code

- VHDL, Verilog, and ModelSim Tcl/Tk DO file test bench options

#### FDATool Plug-In — the GUI

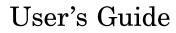

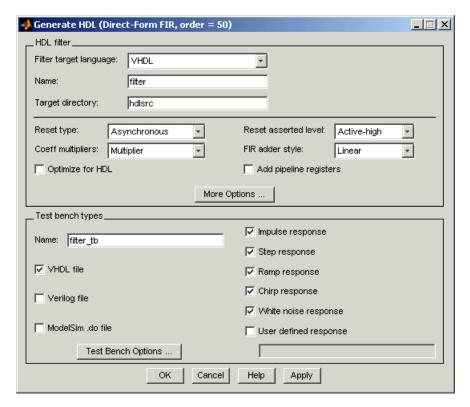

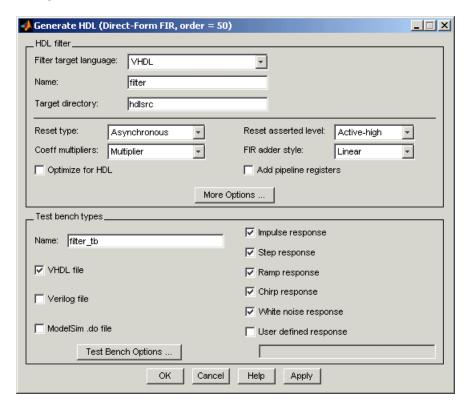

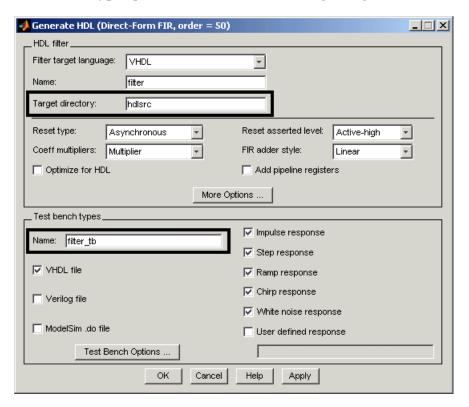

The Filter Design HDL Coder graphical user interface (GUI) is a plug-in component of the FDATool and is accessible from the FDATool **Targets** menu. Given that you have designed, or at least opened, a quantized filter in the FDATool, you can generate HDL code for that filter with the **Generate HDL** dialog. To open this dialog, click **Targets->Generate HDL**. The main dialog appears, showing the title **Generate HDL** and the filter's structure and order. The following dialog indicates that the input is a Direct Form II transposed filter with an order of 50.

Chapter 3, "Generating HDL Code for a Filter Design" explains how to use the GUI to customize HDL code generation to meet project-specific requirements.

#### **Command-Line Interface**

You also have the option of generating HDL code for a filter with the Filter Design HDL Coder command-line interface. You can apply functions interactively at the MATLAB command line or programmatically in an M-file. The following table lists available functions with brief descriptions. For more detail, see Chapter 7, "Functions — Alphabetical List".

| Function           | Purpose                                  |

|--------------------|------------------------------------------|

| generatehdl        | Generate HDL code for quantized filter   |

| generatetb         | Generate test bench for quantized filter |

| generatetbstimulus | Generate and return test bench stimuli   |

#### Quantized Filters — the Input

The input to the Filter Design HDL Coder is a quantized filter that you design and quantize in one of two ways:

- Design and quantize the filter with the Filter Design Toolbox

- Design the filter with the Signal Processing Toolbox and then quantize it with the Filter Design Toolbox

The Filter Design HDL Coder supports the following filter structures:

- Finite impulse response (FIR)

- Antisymmetric FIR

- Transposed FIR

- Symmetric FIR

- Second-order section (SOS) infinite impulse response (IIR) Direct Form I

- SOS IIR Direct Form I transposed

- SOS IIR Direct Form II

- SOS IIR Direct Form II transposed

Each of these structures supports fixed-point, quantization type, and floating-point (double) realizations. The FIR structures also support unsigned fixed-point realizations.

**Note** Filter Design HDL Coder does not support zero order sections for IIR filters.

The quantized filter must have the following data format characteristics:

- Fixed-point signed or unsigned

- Double floating-point precision

For information on how to design filter objects, see the Filter Design Toolbox and Signal Processing Toolbox documentation. For information on quantizing filters, see the Filter Design Toolbox documentation.

#### Filter Properties — Input Parameters

The Filter Design HDL Coder generates filter and test bench HDL code for a specified quantized filter based on the settings of a collection of property name and property value pairs. The properties and their values

- Contribute to the naming of language elements

- Specify port parameters

- Determine the use of advanced HDL coding features

All properties have default settings. However, you can customize the HDL output to meet project specifications by adjusting the property settings with the Filter Design HDL Coder GUI or command line interface. As an FDATool plug-in, the GUI enables you to set properties associated with

- The HDL language specification

- Filename and location specifications

- Reset specifications

- HDL code customizations

- HDL code optimizations

- Test bench customizations

You can set the same filter properties by specifying property name and property value pairs with the functions generatehol, generateb, and generatebstimulus interactively at the MATLAB command line or in M-code.

The property names and property values are *not* case sensitive and, when specifying them, you can abbreviate them to the shortest unique string.

This chapter explains how to apply property settings to customize HDL code generation for a specific application. For lists and descriptions of the properties and functions, see Chapter 5, "Properties — Categorical List" and Chapter 7, "Functions — Alphabetical List", respectively.

#### Generated HDL Files — the Output

Based on the interface you use and the input data you specify, the Filter Design HDL Coder generates filter and filter test bench HDL files as output. If the filter design requires a VHDL package, the Filter Design HDL Coder also generates a package file.

The GUI generates all output files at the end of a dialog session. If you choose to use the command line interface, you generate the filter and test bench HDL files separately with calls to the functions generatehal and generatetb.

By default, the Filter Design HDL Coder places the output files in a subdirectory named hdlsrc, under the current MATLAB directory, and names the files as follows, where *name* is the value of the Name property.

| Language | File                         | Name                   |

|----------|------------------------------|------------------------|

| Verilog  | Filter                       | name.v                 |

|          | Filter test bench            | <pre>name_tb.v</pre>   |

| VHDL     | Filter                       | <i>name</i> .vhd       |

|          | Filter test bench            | <pre>name_tb.vhd</pre> |

|          | Filter package (if required) | <i>name</i> _pkg.vhd   |

#### Installation

The following sections discuss installation:

- "Checking Product Requirements" on page 1-9

- "Installing the Software" on page 1-9

#### **Checking Product Requirements**

Filter Design HDL Coder requires the following:

- MATLAB

- Filter Design Toolbox

- Signal Processing Toolbox

- Fixed-Point Toolbox

#### **Installing the Software**

For information on installing MATLAB, the Signal Processing Toolbox, the Filter Design Toolbox, the Filter Design HDL Coder, and optional software, see the MATLAB installation instructions.

## Getting Help with the Filter Design HDL Coder

The following sections explain how to get help with using the Filter Design HDL Coder:

- "Information Overview" on page 1-10

- "Online Help" on page 1-11

- "Using "What's This?" Context-Sensitive Help" on page 1-11

- "Demos and Tutorials" on page 1-12

#### **Information Overview**

The following information is available with this product:

| Chapter                | 1, "Getting Started"                   | Explains what the product is, how to install it, how you might apply it to the hardware design process, and how to gain access to product documentation and online help. |

|------------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -                      | 2, "Tutorials —<br>ng HDL Code for     | Guides you through the process of generating HDL code for a sampling of filters.                                                                                         |

| -                      | 3, "Generating HDL<br>a Filter Design" | Explains how to use the Filter Design HDL Coder to generate HDL code for a filter design. Provides details on how HDL code is mapped to MATLAB code and vice versa.      |

| Chapter de Design"     | 4, "Testing a Filter                   | Explains how to apply generated test benches.                                                                                                                            |

| Chapter :<br>Categoric | 5, "Properties —<br>eal List"          | Lists filter properties by category.                                                                                                                                     |

Chapter 6, "Properties — Provides descriptions of properties organized alphabetically by property name.

Chapter 7, "Functions — Provides descriptions of the functions available in the product's command line

interface.

#### **Online Help**

The following online help is available:

- Online help in the MATLAB Help browser. Click the Filter Design HDL Coder product link in the browser's Contents pane.

- Context-sensitive "What's This?" help for items that appear in the Filter Design HDL Coder GUI. Click a GUI Help button or right-click on a GUI item or within a specific frame in a GUI dialog to display help on that dialog, item, or frame. For more information on using the context-sensitive help, see "Using "What's This?" Context-Sensitive Help" on page 1-11.

- M-help for the command line interface functions generatehdl, generatetb, andgeneratetbstimulus is accessible with the MATLAB doc and help commands. For example

doc generatehdl help generatehdl

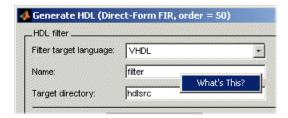

### Using "What's This?" Context-Sensitive Help

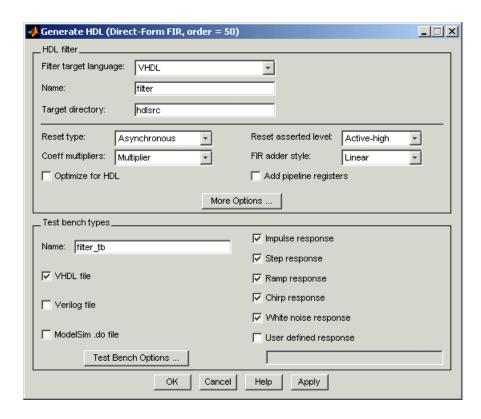

"What's This?" context-sensitive help topic is available for each dialog, pane, and option in the Filter Design HDL Coder GUI. Use the "What's This?" help as needed while using the GUI to configure options that control the contents and style of the generated HDL code and test bench.

To use the "What's This?" help, do the following:

1 Place your cursor over the label or control for an option or in the background for a pane or dialog.

2 Right-click. A **What's This?** button appears. The following display shows the **What's This?** button appearing after a right-click on the **Name** option in the **HDL filter** pane of the **Generate HDL** dialog.

**3** Click **What's This?** The Filter Design HDL Coder opens context-sensitive help that describes the option, pane, or dialog.

#### **Demos and Tutorials**

The Filter Design HDL Coder provides demos and tutorials to help you get started. The demos give you a quick view of the product's capabilities and examples of how you might apply the product. You can run them with limited product exposure.

The tutorials provide procedural instruction on how to apply product features. The following topics, in Chapter 2, "Tutorials — Generating HDL Code for Filters", guide you through three tutorials:

- "Basic FIR Filter Tutorial" on page 2-3

- "Optimized FIR Filter Tutorial" on page 2-23

- "IIR Filter Tutorial" on page 2-43

# Applying the Filter Design HDL Coder to the Hardware Design Process

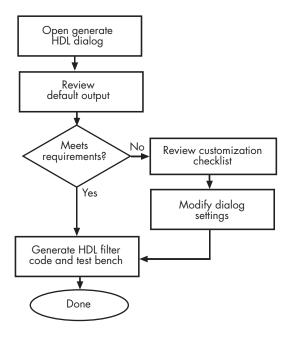

The basic workflow for applying the Filter Design HDL Coder to the hardware design process involves the following steps:

- 1 Design a filter with the Signal Processing or Filter Design Toolbox.

- **2** Quantize the filter with the Filter Design Toolbox.

- **3** Review the property settings that the Filter Design HDL Coder applies to generated HDL code by default.

- **4** Adjust property settings to customize the generated HDL code, as necessary.

- **5** Generate the filter and test bench code.

- **6** Consider and, if appropriate, apply optimization options.

- **7** Test the generated code in a simulation.

The following figure shows these steps in a flow diagram.

# Tutorials — Generating **HDL Code for Filters**

This chapter guides you through the basic steps for generating and testing HDL code for a few filter designs. Topics include the following:

"Creating a Directory for Your Tutorial Files" (p. 2-2)

Suggests that you create a directory to store files generated as you complete the tutorials presented in

this chapter

"Basic FIR Filter Tutorial" (p. 2-3)

Guides you through the steps for designing a basic FIR filter, generating VHDL code for the filter, and verifying the VHDL code with a

generated test bench

"Optimized FIR Filter Tutorial" (p. 2-23)

Guides you through the steps for designing an optimized FIR filter, generating Verilog code for the filter, and verifying the Verilog code with a generated test bench

"IIR Filter Tutorial" (p. 2-43)

Guides you through the steps for designing an IIR filter, generating VHDL code for the filter, and verifying the VHDL code with a

generated test bench

## **Creating a Directory for Your Tutorial Files**

Set up a writable working directory outside the scope of your MATLAB installation area to store files that will be generated as you complete your Filter Design HDL Coder tutorial work. The tutorial instructions assume that you create the directory hdlfilter tutorials on drive D.

#### **Basic FIR Filter Tutorial**

This section guides you through the steps for designing a basic quantized discrete-time FIR filter, generating VHDL code for the filter, and verifying the VHDL code with a generated test bench. The procedure is presented in the following topics:

- "Designing a Basic FIR Filter" on page 2-3

- "Quantizing the Basic FIR Filter" on page 2-5

- "Configuring and Generating the Basic FIR Filter's VHDL Code" on page 2-8

- "Getting Familiar with the Basic FIR Filter's Generated VHDL Code" on page 2-15

- "Verifying the Basic FIR Filter's Generated VHDL Code" on page 2-16

#### **Designing a Basic FIR Filter**

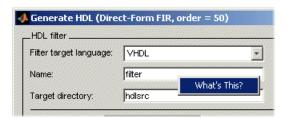

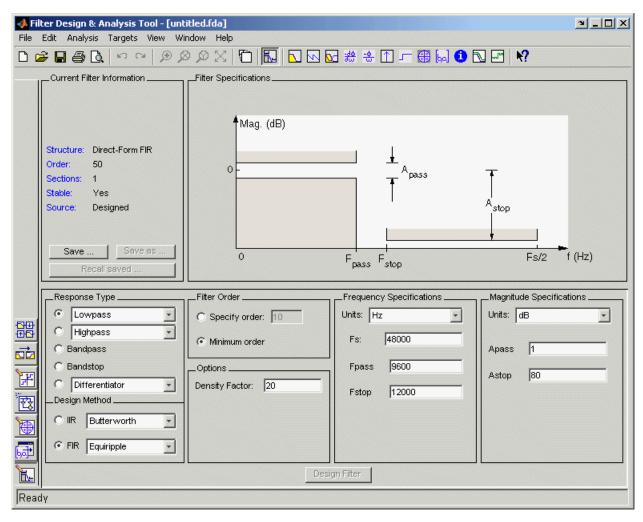

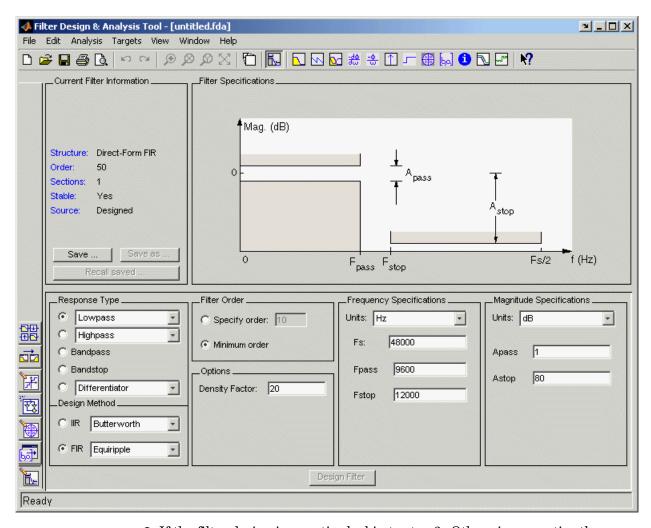

One way of designing a filter in the MATLAB environment is to use the FDATool. This section guides you through the procedure of designing and creating a filter for a basic FIR filter. These instructions assume you are familiar with the MATLAB user interface and the FDATool.

- 1 Start MATLAB.

- **2** Set your MATLAB current directory to the directory you created in "Creating a Directory for Your Tutorial Files" on page 2-2.

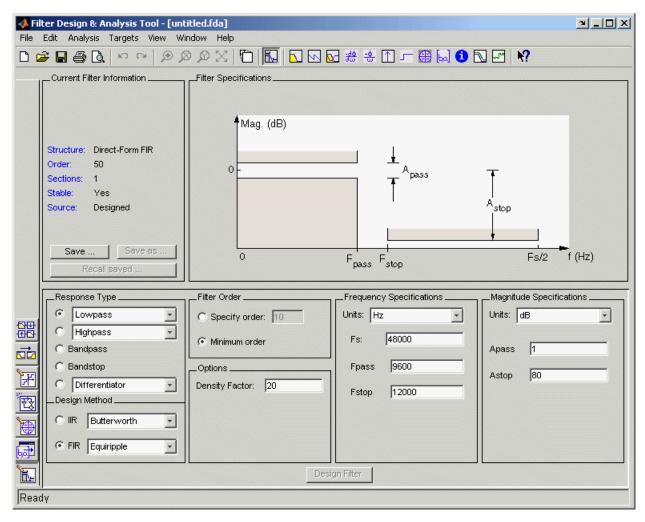

- 3 Start the FDATool by entering the fdatool command in the MATLAB Command Window. MATLAB displays the Filter Design & Analysis Tool dialog.

4 In the Filter Design & Analysis Tool dialog, check that the following filter options are set:

| Option        | Value          |  |

|---------------|----------------|--|

| Response Type | Lowpass        |  |

| Design Method | FIR Equiripple |  |

| Option                   | Value              |

|--------------------------|--------------------|

| Filter Order             | Minimum order (50) |

| Options                  | Density Factor: 20 |

| Frequency Specifications | Units: Hz          |

|                          | Fs: 48000          |

|                          | Fpass: 9600        |

|                          | Fstop: 12000       |

| Magnitude Specifications | Units: dB          |

|                          | Apass: 1           |

|                          | Astop: 80          |

These settings are for the default filter design that the FDATool creates for you. If you do not need to make any changes and **Design Filter** is greyed out, you are done and can skip to "Quantizing the Basic FIR Filter" on page 2-5.

5 If you modified any of the options listed in step 4, click **Design Filter**. The FDATool creates a filter for the specified design and displays the following message in the FDATool status bar when the task is complete.

```

Designing Filter... Done

```

For more information on designing filters with the FDATool, see the FDATool and Filter Design Toolbox documentation.

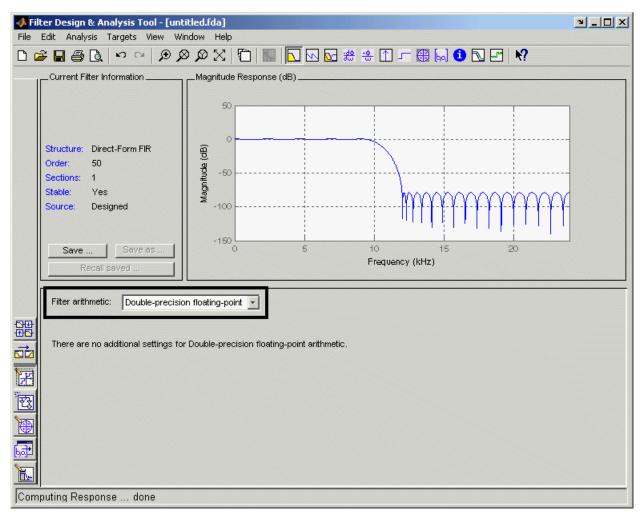

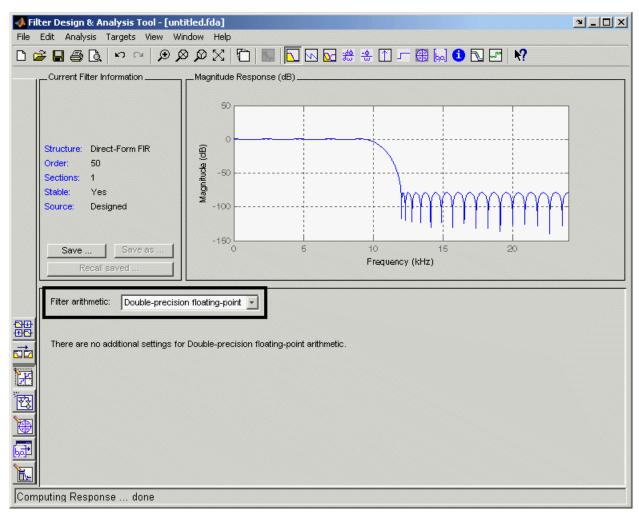

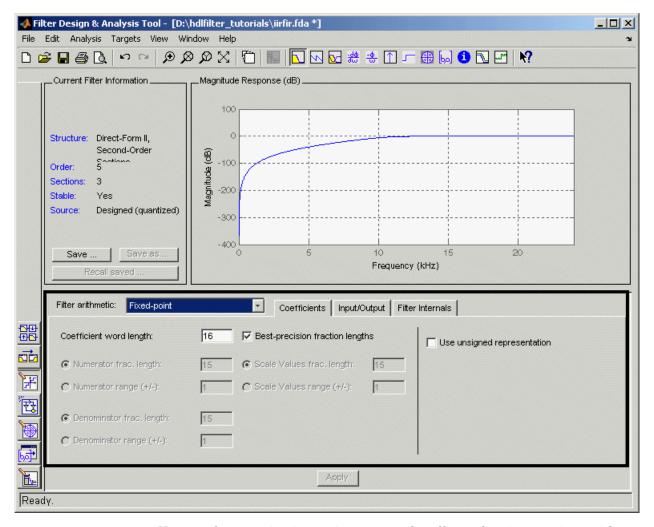

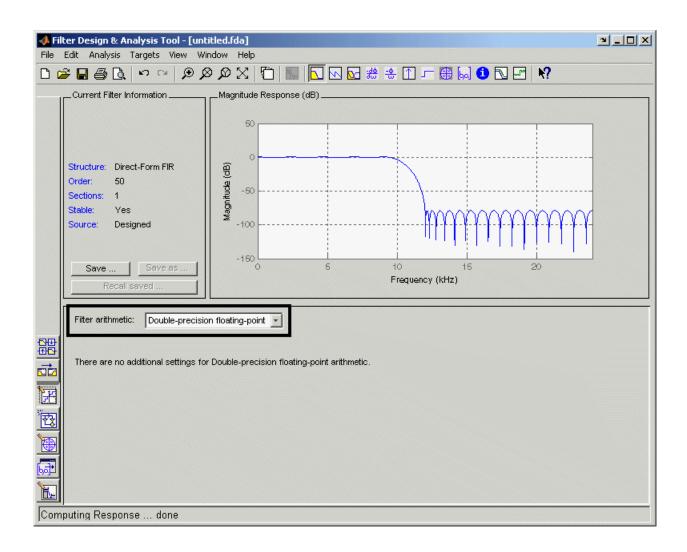

#### **Quantizing the Basic FIR Filter**

You should quantize filters for HDL code generation. To quantize your filter,

- 1 Open the basic FIR filter design you created in "Designing a Basic FIR Filter" on page 2-3 if it is not already open.

- 2 Click the **Set quantization parameters** icon in the left-side tool bar. The FDATool displays a **Filter arithmetic** menu in the bottom half of its dialog.

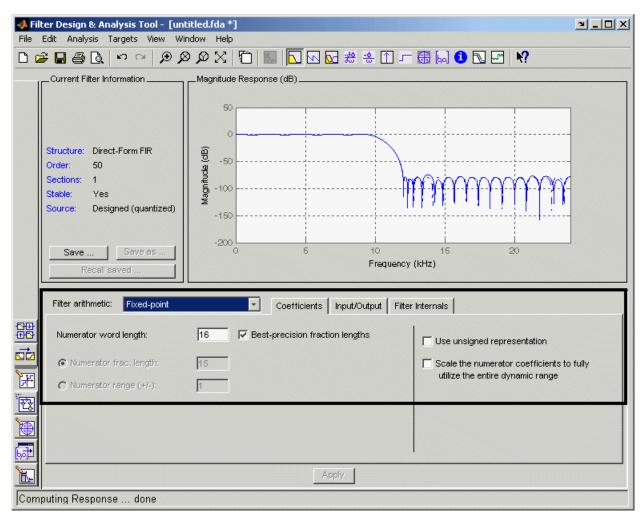

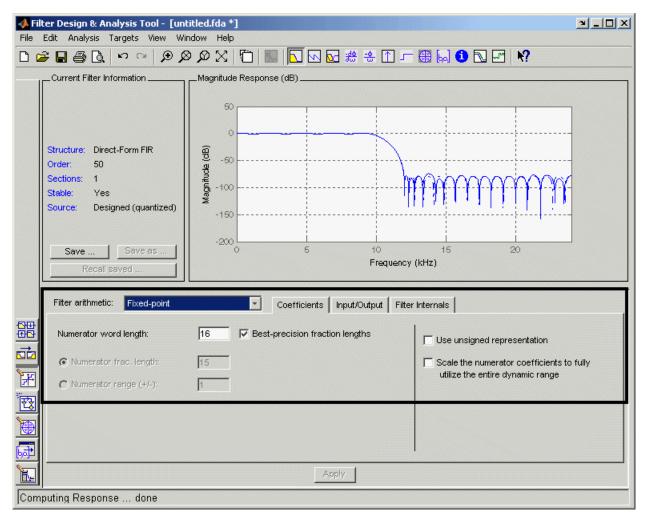

3 Select Fixed-point from the Filter arithmetic menu. The FDATool displays the first of three tabbed panels of quantization parameters across the bottom half of its dialog.

You use the quantization options to test the effects of various settings with a goal of optimizing the quantized filter's performance and accuracy.

**4** Set the quantization parameters as follows:

| Tab              | Parameter                                                                  | Setting           |

|------------------|----------------------------------------------------------------------------|-------------------|

| Coefficients     | Numerator word length                                                      | 16                |

|                  | Best-precision fraction lengths                                            | Selected          |

|                  | Use unsigned representation                                                | Cleared           |

|                  | Scale the numerator coefficients to fully utilize the entire dynamic range | Cleared           |

| Input/Output     | Input word length                                                          | 16                |

|                  | Input fraction length                                                      | 15                |

|                  | Output word length                                                         | 16                |

|                  | Avoid overflow                                                             | Selected          |

| Filter Internals | Round towards                                                              | Floor             |

|                  | Overflow mode                                                              | Saturate          |

|                  | Product mode                                                               | Full<br>precision |

|                  | Accum. mode                                                                | Keep MSB          |

|                  | Accum. word length                                                         | 40                |

|                  | Cast signals before accum.                                                 | Selected          |

#### 5 Click Apply.

For more information on quantizing filters, see the FDATool and Filter Design Toolbox documentation.

#### Configuring and Generating the Basic FIR Filter's VHDL Code

After you quantize your filter, you are ready to use the Filter Design HDL Coder to configure and generate the filter's VHDL code. This section guides you through the procedure for starting the Filter Design HDL Coder GUI, setting some options, and generating the VHDL code and a test bench for the basic FIR filter you designed and quantized in "Designing a Basic FIR Filter" on page 2-3 and "Quantizing the Basic FIR Filter" on page 2-5.

1 Start the Filter Design HDL Coder by clicking Targets->Generate HDL in the FDATool dialog. The FDATool displays the Filter Design HDL Coder dialog.

- **2** Find the Filter Design HDL Coder online help. Use the help to learn about product details or to get answers to questions as you work with the designer.

- a In the MATLAB window, click the **Help icon** in the toolbar or click **Help->Full Product Family Help**.

- b In the Help browser's Contents pane, select Filter Design HDL Coder.

- c Minimize the Help browser.

- 3 Click the **Help** button. The FDATool displays context-sensitive help for the dialog. As necessary, use the **Help** button on the other Filter Design HDL Coder dialogs for context-sensitive help on those dialog views.

- **4** Close the Help window.

- 5 Place your cursor over the **Name** label or text box in the **HDL filter** pane of the Generate HDL dialog and right-click. A What's This? button appears.

- 6 Click What's This? The Filter Design HDL Coder opens context-sensitive help that describes the **Name** option. Use the context-sensitive help as needed while using the GUI to configure options that control the contents and style of the generated HDL code and test bench. A help topic is available for each option and pane.

- 7 In the Name text box of the HDL filter pane, replace the default name with basicfir. This option names the VHDL entity and the file that is to contain the filter's VHDL code.

- 8 In the Name text box of the **Test bench types** pane, replace the default name with basicfir tb. This option names the generated test bench file.

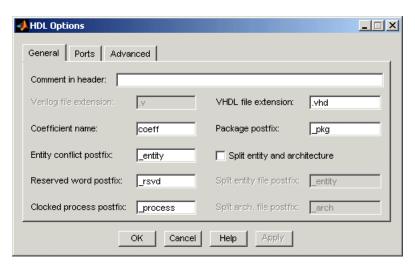

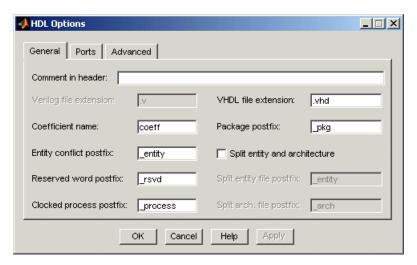

- 9 Click More Options. The Filter Design HDL Coder displays an HDL **Options** dialog.

- 10 In the Comment in header text box, type Tutorial Basic FIR Filter and then click Apply. The Filter Design HDL Coder adds the comment to the end of the header comment block in each generated file.

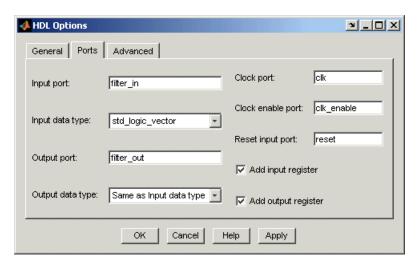

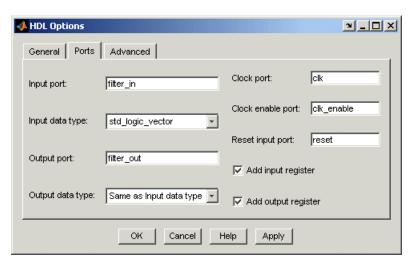

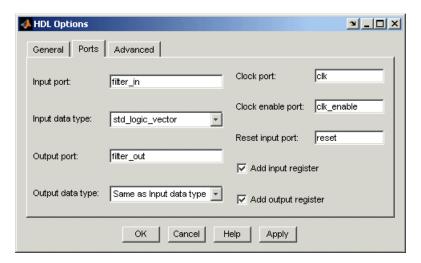

- 11 Click the **Ports** tab. The **Ports** pane appears.

12 Change the names of the input and output ports. Replace filter\_in with data\_in and filter\_out with data\_out.

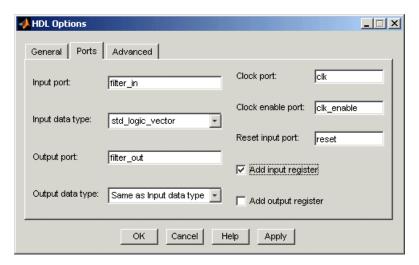

13 Clear the check box for the Add input register option. The Ports tab should now look like the following.

- 14 Click Apply and then OK to register your changes and close the HDL Options dialog.

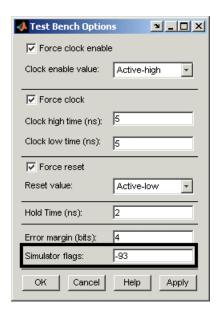

- 15 Click Test Bench Options. The Filter Design HDL Coder displays a Test Bench Options dialog.

You use this dialog to customize the generated test bench.

- **16** For this tutorial, apply the default settings by clicking **OK**.

- 17 In the **Generate HDL** dialog, click **Apply** or **OK** to start the code generation process. **OK** closes the dialog.

The Filter Design HDL Coder displays the following messages in the MATLAB Command Window as it generates the filter and test bench VHDL files:

```

### Starting VHDL code generation process for filter: basicfir

### Generating basicfir.vhd file in: hdlsrc

### Starting generation of basicfir VHDL entity

### Starting generation of basicfir VHDL architecture

### Successful completion of VHDL code generation process for

filter: basicfir

### Starting generation of VHDL Test Bench

### Generating input stimulus

### Done generating input stimulus; length 3429 samples.

### Generating VHDL file basicfir_tb.vhd in: hdlsrc

### Done generating VHDL test bench.

```

As the messages indicate, the Filter Design HDL Coder creates the directory hdlsrc under your current working directory and places the files basicfir.vhd and basicfir tb.vhd in that directory.

The generated VHDL code has the following characteristics:

- VHDL entity named basicfir.

- Registers that use asynchronous resets when the reset signal is active high (1).

- Ports have the following names:

| VHDL Port          | Name       |

|--------------------|------------|

| Input              | data_in    |

| Output             | data_out   |

| Clock input        | clk        |

| Clock enable input | clk_enable |

| Reset input        | reset      |

- An extra register for handling filter output.

- Clock input, clock enable input and reset ports are of type STD LOGIC and data input and output ports are of type STD LOGIC VECTOR.

- Coefficients are named coeffn, where *n* is the coefficient number, starting with 1.

- Type safe representation is used when zeros are concatenated: '0' & '0'...

- Registers are generated with the statement ELSIF clk'event AND clk='1' THEN rather than with the rising edge function.

- The postfix string process is appended to process names.

The generated test bench:

- Is a portable VHDL file.

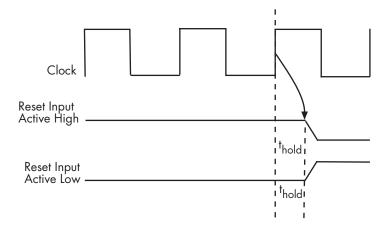

- Forces clock, clock enable, and reset input signals.

- Forces the clock enable input signal to active high.

- Drives the clock input signal high (1) for 5 nanoseconds and low (0) for 5 nanoseconds.

- Forces the reset signal for two cycles plus a hold time of 2 nanoseconds.

- Applies a hold time of 2 nanoseconds to data input signals.

- Applies impulse, step, ramp, chirp, and white noise stimulus types.

## Getting Familiar with the Basic FIR Filter's Generated VHDL Code

Get familiar with the filter's generated VHDL code by opening and browsing through the file basicfir.vhd in an ASCII or HDL simulator editor.

- 1 Open the generated VHDL filter file basicfir.vhd.

- **2** Search for basicfir. This line identifies the VHDL module, using the string you specified for the **Name** option in the **HDL filter** pane. See step 5 in "Configuring and Generating the Basic FIR Filter's VHDL Code" on page 2-8.

- **3** Search for Tutorial. This is where the Filter Design HDL Coder places the text you entered for the **Comment in header** option. See step 10 in "Configuring and Generating the Basic FIR Filter's VHDL Code" on page 2-8.

- **4** Search for HDL Code. This section lists the Filter Design HDL Coder options you modified in "Configuring and Generating the FIR Filter's Optimized Verilog Code" on page 2-28.

- **5** Search for Filter Settings. This section describes the filter design and quantization settings as you specified in "Designing a Basic FIR Filter" on page 2-3 and "Quantizing the Basic FIR Filter" on page 2-5.

- **6** Search for ENTITY. This line names the VHDL entity, using the string you specified for the **Name** option in the **HDL filter** pane. See step 5 in "Configuring and Generating the Basic FIR Filter's VHDL Code" on page 2-8.

- 7 Search for PORT. This PORT declaration defines the filter's clock, clock enable, reset, and data input and output ports. The ports for clock, clock enable, and reset signals are named with default strings. The ports for data input and output are named with the strings you specified for the **Input port** and **Output port** options on the **Ports** tab of the **HDL Options**

- dialog. See step 12 in "Configuring and Generating the Basic FIR Filter's VHDL Code" on page 2-8.

- 8 Search for Constants. This is where the coefficients are defined. They are named using the default naming scheme, coeffn, where n is the coefficient number, starting with 1.

- **9** Search for Signals. This is where the filter's signals are defined.

- 10 Search for process. The PROCESS block name Delay Pipeline process includes the default PROCESS block postfix string process.

- 11 Search for IF reset. This is where the reset signal is asserted. The default, active high (1), was specified. Also note that the PROCESS block applies the default asynchronous reset style when generating VHDL code for registers.

- 12 Search for ELSIF. This is where the VHDL code checks for rising edges when the filter operates on registers. The default ELSIF clk'event statement is used instead of the optional rising edge function.

- 13 Search for Output Register. This is where filter output is written to an output register. The Filter Design HDL Coder generates the code for this register by default. In step 13 in "Configuring and Generating the Basic FIR Filter's VHDL Code" on page 2-8, you cleared the **Add input** register option, but left the Add output register selected. Also note that the PROCESS block name Output Register process includes the default PROCESS block postfix string process.

- **14** Search for data out. This is where the filter writes its output data.

## Verifying the Basic FIR Filter's Generated VHDL Code

This section explains how to verify the basic FIR filter's generated VHDL code with the generated VHDL test bench. Although this tutorial uses ModelSim as the tool for compiling and simulating the VHDL code, you can use any VHDL simulation tool package.

To verify the filter code, complete the following steps:

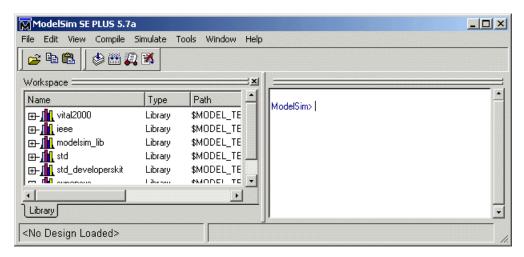

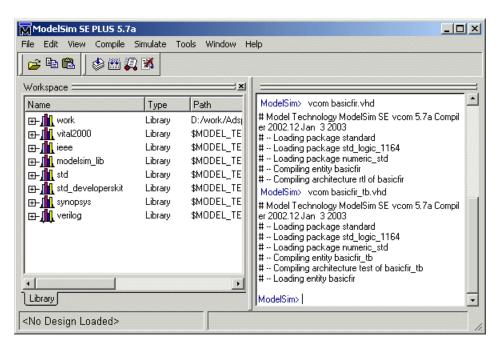

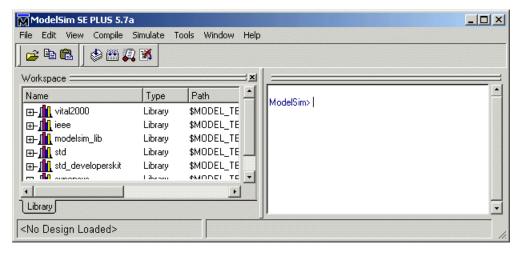

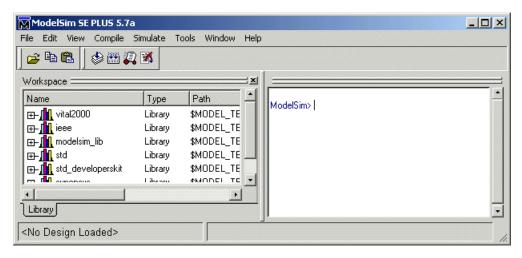

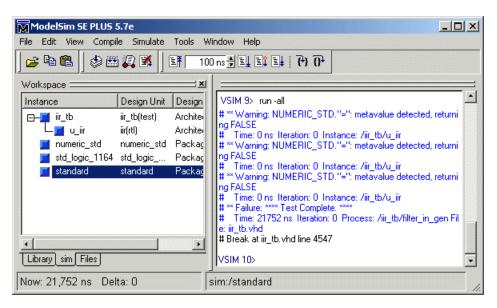

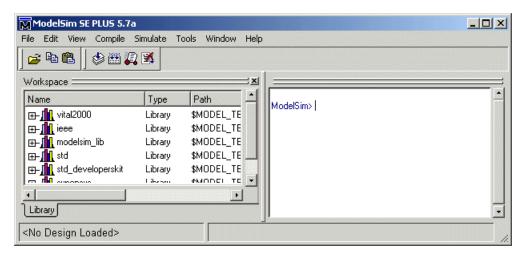

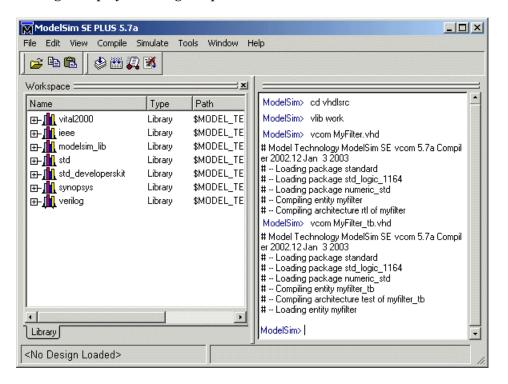

1 Start your simulator. When you start ModelSim, a screen display similar to the following appears.

**2** Set the current directory to the directory that contains your generated VHDL files. For example:

```

cd d:/hdlfilter tutorials/hdlsrc

```

**3** If necessary, create a design library to store the compiled VHDL entities, packages, architectures, and configurations. In ModelSim, you can create a design library with the vlib command.

```

vlib work

```

**4** Compile the generated filter and test bench VHDL files. In ModelSim, you compile VHDL code with the vcom command. The following ModelSim commands compile the filter and filter test bench VHDL code.

```

vcom basicfir.vhd

vcom basicfir_tb.vhd

```

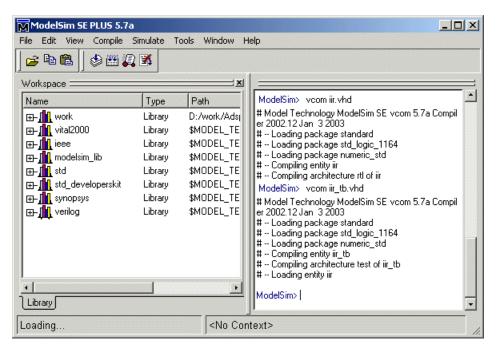

The following screen display shows this command sequence and informational messages displayed during compilation.

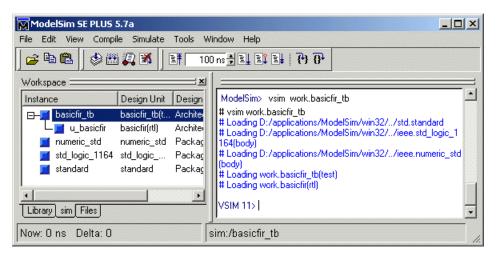

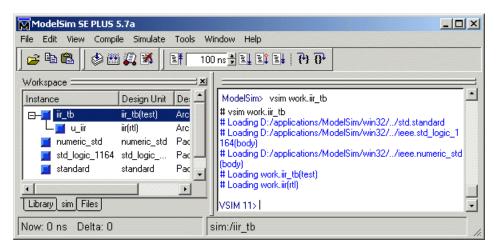

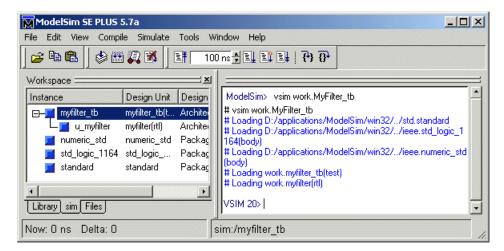

**5** Load the test bench for simulation. The procedure for doing this varies depending on the simulator you are using. In ModelSim, you load the test bench for simulation with the vsim command. For example:

vsim work.basicfir tb

The following ModelSim display shows the results of loading work.basicfir\_tb with the vsim command.

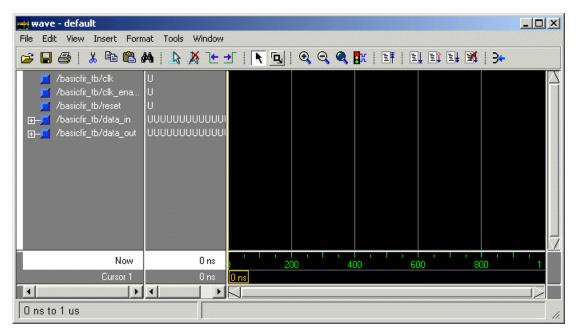

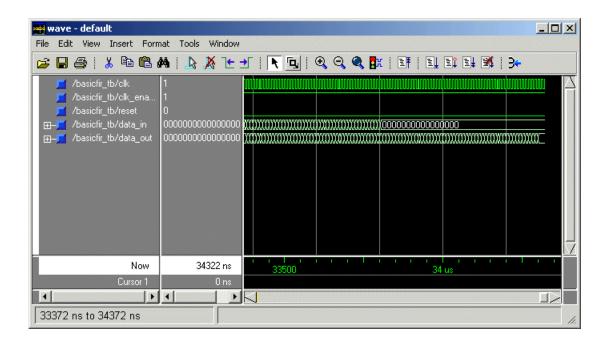

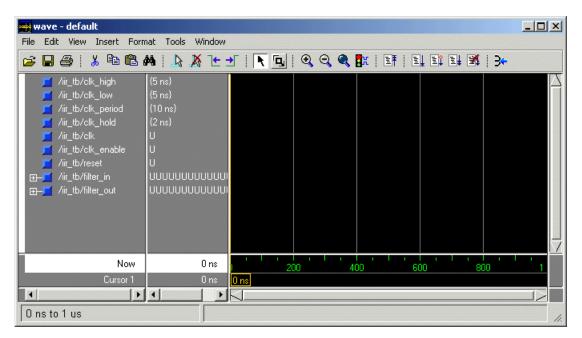

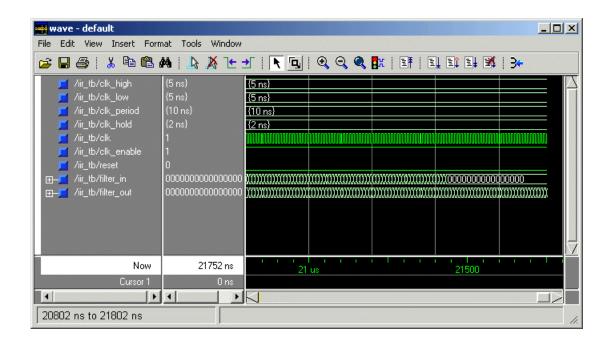

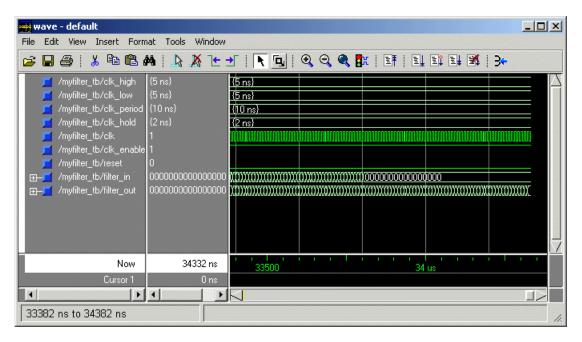

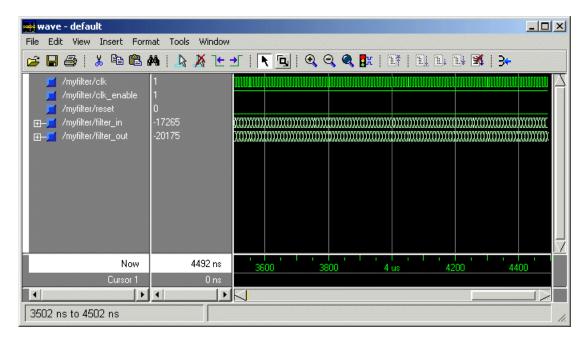

**6** Open a display window for monitoring the simulation as the test bench runs. For example, in ModelSim, you can use the following command to open a **wave** window to view the results of the simulation as HDL waveforms:

add wave \*

The following Wave window displays.

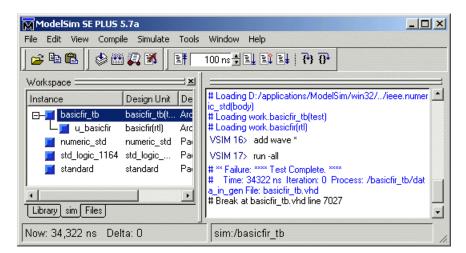

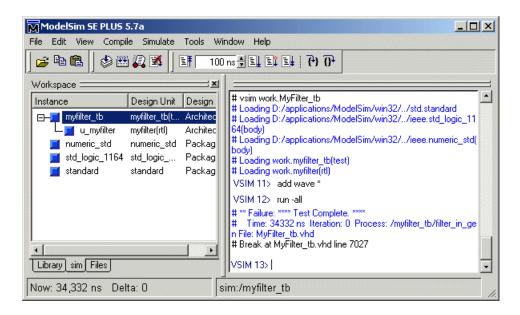

7 To start running the simulation, issue the appropriate command for your simulator. For example, in ModelSim, you can start a simulation with the run command.

The following ModelSim display shows the run -all command being used to start a simulation.

As your test bench simulation runs, watch for error messages. If any error messages appear, you must interpret them as they pertain to your filter design and the HDL customizations you applied with the Filter Design HDL Coder. You must determine whether the results are expected based on the customizations you specified when generating the filter VHDL code.

**Note** The failure message that appears in the preceding display is not flagging an error. If the message includes the string Test Complete, the test bench has successfully run to completion. The Failure part of the message is tied to the mechanism the Filter Design HDL Coder uses to end the simulation.

The following Wave window shows the simulation results as HDL waveforms.

## **Optimized FIR Filter Tutorial**

This section guides you through the steps for designing an optimized quantized discrete-time FIR filter, generating Verilog code for the filter, and verifying the Verilog code with a generated test bench. The procedure is presented in the following topics:

- "Designing the FIR Filter" on page 2-23

- "Quantizing the FIR Filter" on page 2-25

- "Configuring and Generating the FIR Filter's Optimized Verilog Code" on page 2-28

- "Getting Familiar with the FIR Filter's Optimized Generated Verilog Code" on page 2-35

- "Verifying the FIR Filter's Optimized Generated Verilog Code" on page 2-37

## **Designing the FIR Filter**

One way of designing a filter in the MATLAB environment is to use the FDATool. This section guides you through the procedure of designing and creating a filter for an FIR filter to which you will apply VHDL optimizations. These instructions assume you are familiar with the MATLAB user interface and the FDATool.

- 1 Start MATLAB.

- **2** Set your MATLAB current directory to the directory you created in "Creating a Directory for Your Tutorial Files" on page 2-2.

- 3 Start the FDATool by entering the fdatool command in the MATLAB Command Window. MATLAB displays the **Filter Design & Analysis Tool** dialog.

4 In the Filter Design & Analysis Tool dialog, set the following filter options:

| Option        | Value          |

|---------------|----------------|

| Response Type | Lowpass        |

| Design Method | FIR Equiripple |

| Option                   | Value              |

|--------------------------|--------------------|

| Filter Order             | Minimum order (50) |

| Options                  | Density Factor: 20 |

| Frequency Specifications | Units: Hz          |

|                          | Fs: 48000          |

|                          | Fpass: 9600        |

|                          | Fstop: 12000       |

| Magnitude Specifications | Units: dB          |

|                          | Apass: 1           |

|                          | Astop: 80          |

These are settings are for the default filter design that the FDATool creates for you. If you do not need to make any changes and **Design Filter** is greyed out, you are done and can skip to "Quantizing the FIR Filter" on page 2-25.

**5** Click **Design Filter**. The FDATool creates a filter for the specified design. The following message appears in the FDATool status bar when the task is complete.

Designing Filter... Done

For more information on designing filters with the FDATool, see the FDATool and Filter Design Toolbox documentation.

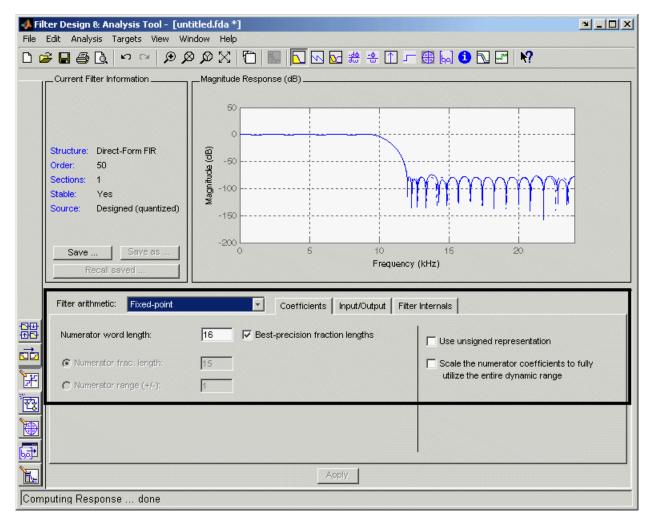

### **Quantizing the FIR Filter**

You should quantize filters for HDL code generation. To quantize your filter,

- 1 Open the FIR filter design you created in if it is not already open.

- 2 Click the **Set quantization parameters** icon in the left-side tool bar. The FDATool displays a **Filter arithmetic** menu in the bottom half of its dialog.

3 Select Fixed-point from the menu. The FDATool displays the first of three tabbed panels of quantization parameters across the bottom half of its dialog.

You use the quantization options to test the effects of various settings with a goal of optimizing the quantized filter's performance and accuracy.

**4** Set the quantization parameters as follows:

| Tab              | Parameter                                                                  | Setting           |

|------------------|----------------------------------------------------------------------------|-------------------|

| Coefficients     | Numerator word length                                                      | 16                |

|                  | Best-precision fraction lengths                                            | Selected          |

|                  | Use unsigned representation                                                | Cleared           |

|                  | Scale the numerator coefficients to fully utilize the entire dynamic range | Cleared           |

| Input/Output     | Input word length                                                          | 16                |

|                  | Input fraction length                                                      | 15                |

|                  | Output word length                                                         | 16                |

|                  | Avoid overflow                                                             | Selected          |

| Filter Internals | Round towards                                                              | Floor             |

|                  | Overflow mode                                                              | Saturate          |

|                  | Product mode                                                               | Full<br>precision |

|                  | Accum. mode                                                                | Keep MSB          |

|                  | Accum. word length                                                         | 40                |

|                  | Cast signals before accum.                                                 | Set               |

#### 5 Click Apply.

For more information on quantizing filters, see the FDATool and Filter Design Toolbox documentation.

## Configuring and Generating the FIR Filter's Optimized **Verilog Code**

After you quantize your filter, you are ready to use the Filter Design HDL Coder to configure and generate the filter's Verilog code. This section guides you through the process for starting the Filter Design HDL Coder GUI, setting some options, and generating the Verilog code and a test bench for the FIR filter you designed and quantized in "Designing the FIR Filter" on page 2-23 and "Quantizing the FIR Filter" on page 2-25.

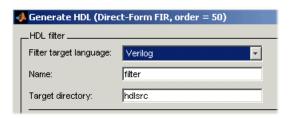

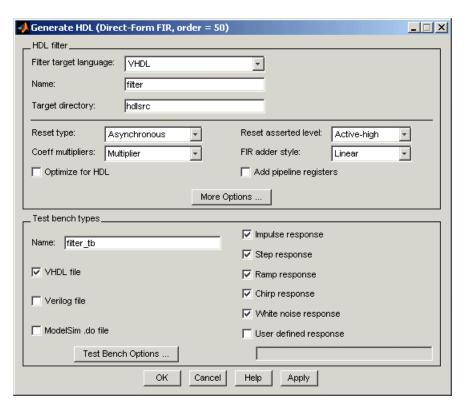

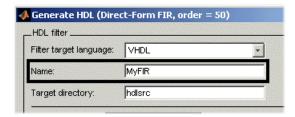

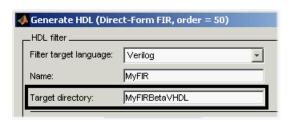

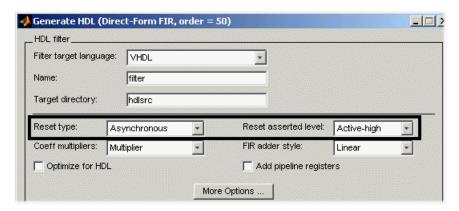

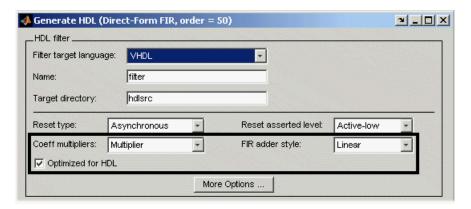

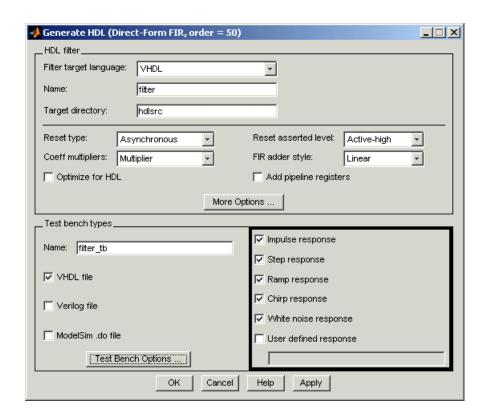

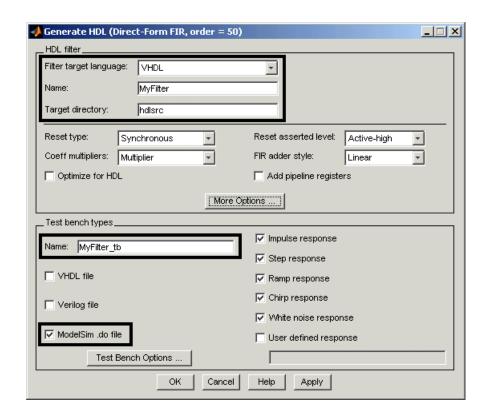

1 Start the Filter Design HDL Coder by clicking **Targets->Generate HDL** in the FDATool dialog. The FDATool displays the Filter Design HDL Coder dialog.

| Generate HDL (Direct-Form FIR, order = 5 | 50)                               |

|------------------------------------------|-----------------------------------|

| HDL filter                               |                                   |

| Filter target language: VHDL             | v                                 |

| Name: filter                             |                                   |

| Target directory: hdlsrc                 |                                   |

| Reset type: Asynchronous                 | Reset asserted level: Active-high |

| Coeff multipliers: Multiplier            | FIR adder style: Linear 🔻         |

| Optimize for HDL                         | Add pipeline registers            |

| More Options                             |                                   |

| Test bench types                         |                                   |

| Name: filter_tb                          | ✓ Impulse response                |

| niter_to                                 | ✓ Step response                   |

| ▼ VHDL file                              | ▼ Ramp response                   |

| ☐ Verilog file                           | ✓ Chirp response                  |

| yerlog lie                               | ✓ White noise response            |

| ModelSim .do file                        | User defined response             |

| Test Bench Options                       |                                   |

| OK Cancel Help Apply                     |                                   |

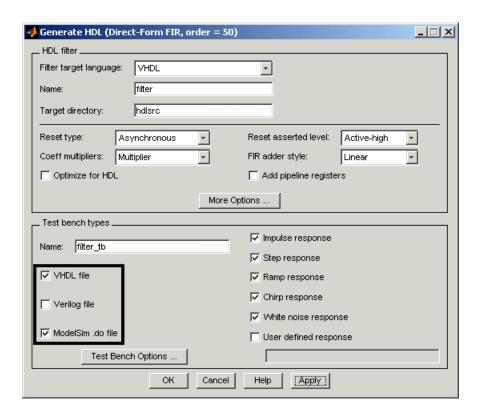

2 Select Verilog for the **Filter target language** option, as shown in the following dialog.

- 3 In the Name text box of the HDL filter pane, replace the default name with optfir. This option names the Verilog module and the file that is to contain the filter's Verilog code.

- **4** In the **Name** text box of the **Test bench types** pane, replace the default name with optfir tb. This option names the generated test bench file.

- 5 In the HDL filter pane, select the Optimize for HDL option. This option is for generating HDL code that is optimized for performance or space requirements. When this option is enabled, the Filter Design HDL Coder makes tradeoffs concerning data types and might ignore your quantization settings to achieve optimizations. When you use the option, keep in mind that you do so at the cost of potential numeric differences between filter results produced by MATLAB and the simulated results for the optimized HDL code.

- **6** Select CSD for the **Coeff multipliers** option. This option optimizes coefficient multiplier operations by instructing the coder to replace them with additions of partial products produced by a canonic signed digit (CSD) technique. This technique minimizes the number of addition operations required for constant multiplication by representing binary numbers with a minimum count of nonzero digits. This option also has the potential for producing numeric differences between MATLAB filter results and the simulated results for the optimized HDL code.

- 7 Select the **Add pipeline registers** option. For FIR filters, this option optimizes final summation. The coder creates a final adder that performs pair-wise addition on successive products and includes a stage of pipeline registers after each level of the tree. When used for FIR filters, this option also has the potential for producing numeric differences between MATLAB filter results and the simulated results for the optimized HDL code.

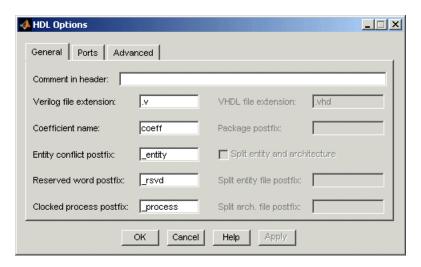

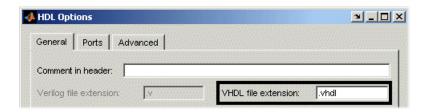

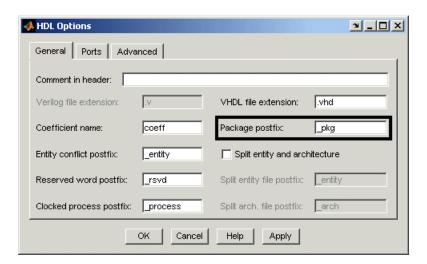

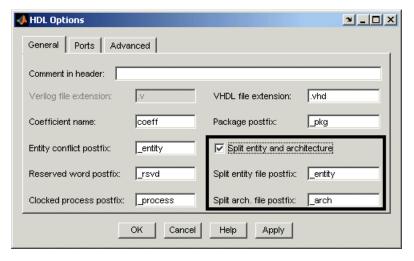

- 8 Click More Options. The Filter Design HDL Coder displays an HDL Options dialog.

- **9** In the **Comment in header** text box, type Tutorial Optimized FIR Filter and then click **Apply**. The Filter Design HDL Coder adds the comment to the end of the header comment block in each generated file.

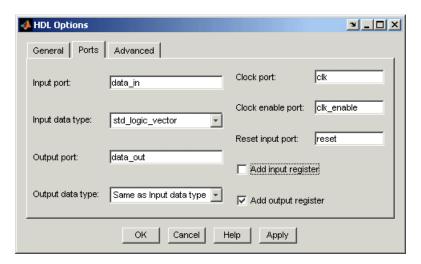

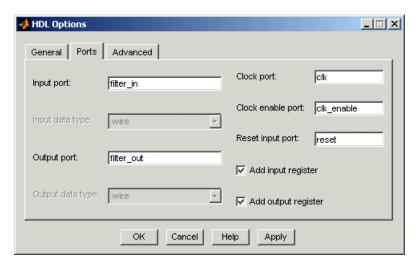

- **10** Click the **Ports** tab. The **Ports** appears.

11 Change the names of the input and output ports. Replace filter\_in with data\_in and filter\_out with data\_out.

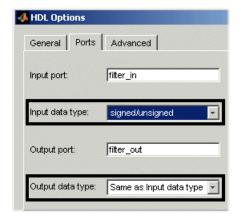

12 Clear the check box for the Add input register option. The Ports tab should now look like the following.

- 13 Click Apply and then OK to register your changes and close the HDL **Options** dialog.

- 14 Click **Test Bench Options**. The Filter Design HDL Coder displays a Test Bench Options dialog.

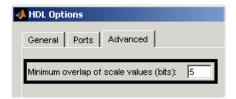

Use this dialog to customize the generated test bench. Note that the **Error margin (bits)** option is enabled. This is due to the use of optimization options that potentially produce numeric results that differ from the results of the original MATLAB filter. You can use this option to adjust the number of least significant bits the test bench will ignore during comparisons before generating a warning.

- **15** For this tutorial, apply the default settings by clicking **OK**.

- **16** In the **Generate HDL** dialog, click **Apply** or **OK** to start the code generation process. **OK** closes the dialog.

The Filter Design HDL Coder displays the following messages in the MATLAB Command Window as it generates the filter and test bench Verilog files:

```

### Starting Verilog code generation process for filter: optfir

### Generating optfir.v file in: hdlsrc

### Starting generation of optfir Verilog module

### Starting generation of optfir Verilog module body

### HDL latency is 6 samples

### Successful completion of Verilog code generation process

for filter: optfir

```

```

### Starting generation of Verilog Test Bench

### Generating input stimulus

### Done generating input stimulus; length 3429 samples.

### Generating Verilog file optfir tb.v in: hdlsrc

### Done generating Verilog test bench.

```

As the messages indicate, the Filter Design HDL Coder creates the directory hdlsrc under your current working directory and places the files optfir.v and optfir tb.v in that directory.

The generated Verilog code has the following characteristics:

- Verilog module named optfir.

- Registers that use asynchronous resets when the reset signal is active high (1).

- Generated code that optimizes its use of data types and eliminates redundant operations.

- Coefficient multipliers optimized with the CSD technique.

- Final summations optimized using a pipelined technique.

- Ports that have the following names:

| 1 | /erilog Port       | Name       |

|---|--------------------|------------|

| Ι | nput               | data_in    |

| ( | Output             | data_out   |

| ( | Clock input        | clk        |

| ( | Clock enable input | clk_enable |

| F | Reset input        | reset      |

- An extra register for handling filter output.

- Coefficients named coeffn, where n is the coefficient number, starting with 1.

- Type safe representation is used when zeros are concatenated: '0' & '0'...

The postfix string \_process is appended to sequential (begin) block names.

The generated test bench:

- Is a portable Verilog file.

- Forces clock, clock enable, and reset input signals.

- Forces the clock enable input signal to active high.

- Drives the clock input signal high (1) for 5 nanoseconds and low (0) for 5 nanoseconds.

- Forces the reset signal for two cycles plus a hold time of 2 nanoseconds.

- Applies a hold time of 2 nanoseconds to data input signals.

- Applies an error margin of 4 bits.

- Applies impulse, step, ramp, chirp, and white noise stimulus types.

# Getting Familiar with the FIR Filter's Optimized Generated Verilog Code

Get familiar with the filter's optimized generated Verilog code by opening and browsing through the file optfir.v in an ASCII or HDL simulator editor.

- 1 Open the generated Verilog filter file optcfir.v.

- **2** Search for optfir. This line identifies the Verilog module, using the string you specified for the **Name** option in the **HDL filter** pane. See step 3 in "Configuring and Generating the FIR Filter's Optimized Verilog Code" on page 2-28.

- **3** Search for Tutorial. This is where the Filter Design HDL Coder places the text you entered for the **Comment in header** option. See step 9 in "Configuring and Generating the FIR Filter's Optimized Verilog Code" on page 2-28.

- **4** Search for HDL Code. This section lists the Filter Design HDL Coder options you modified in "Configuring and Generating the FIR Filter's Optimized Verilog Code" on page 2-28.

- **5** Search for Filter Settings. This section of the VHDL code describes the filter design and quantization settings as you specified in "Designing the FIR Filter" on page 2-23 and "Quantizing the FIR Filter" on page 2-25.

- **6** Search for module. This line names the Verilog module, using the string you specified for the **Name** option in the **HDL filter** pane. This line also declares the list of ports, as defined by options on the **Ports** pane of the **HDL Options** dialog. The ports for data input and output are named with the strings you specified for the **Input port** and **Output port** options on the **Ports** tab of the **HDL Options** dialog. See steps 3 and 11 in "Configuring and Generating the FIR Filter's Optimized Verilog Code" on page 2-28.

- **7** Search for input. This line and the four lines that follow, declare the direction mode of each port.

- **8** Search for Constants. This is where the coefficients are defined. They are named using the default naming scheme, coeffn, where n is the coefficient number, starting with 1.

- **9** Search for Signals. This is where the filter's signals are defined.

- 10 Search for sumvector1. This area of code declares the signals for implementing an instance of a pipelined final adder. Signal declarations for four additional pipelined final adders are also included. These signals are used to implement the pipelined FIR adder style optimization specified with the Add pipeline registers option. See step 7 in "Configuring and Generating the FIR Filter's Optimized Verilog Code" on page 2-28.

- 11 Search for process. The block name Delay Pipeline process includes the default block postfix string process.

- 12 Search for reset. This is where the reset signal is asserted. The default, active high (1), was specified. Also note that the process applies the default asynchronous reset style when generating code for registers.

- 13 Search for posedge. This Verilog code checks for rising edges when the filter operates on registers.

- 14 Search for sumdelay pipeline process1. This block implements the pipeline register stage of the pipeline FIR adder style you specified in step 7 of "Configuring and Generating the FIR Filter's Optimized Verilog Code" on page 2-28.

- 15 Search for output register. This is where filter output is written to an output register. The Filter Design HDL Coder generates the code for this register by default. In step 12 in "Configuring and Generating the FIR Filter's Optimized Verilog Code" on page 2-28, you cleared the Add

**input register** option, but left the **Add output register** selected. Also note that the process name Output\_Register\_process includes the default process postfix string process.

16 Search for data out. This is where the filter writes its output data.

# Verifying the FIR Filter's Optimized Generated Verilog Code

This section explains how to verify the FIR filter's optimized generated Verilog code with the generated Verilog test bench. Although this tutorial uses ModelSim as the tool for compiling and simulating the Verilog code, you can use any HDL simulation tool package.

To verify the filter code, complete the following steps:

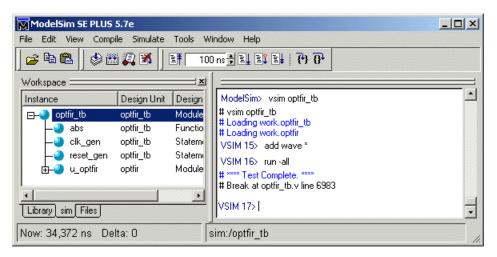

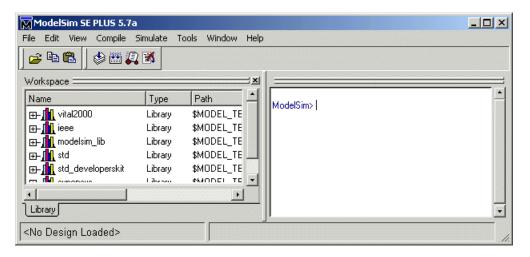

1 Start your simulator. When you start ModelSim, a screen display similar to the following appears.

**2** Set the current directory to the directory that contains your generated Verilog files. For example:

cd hdlsrc

**3** If necessary, create a design library to store the compiled Verilog modules. In ModelSim, you can create a design library with the vlib command.

vlib work

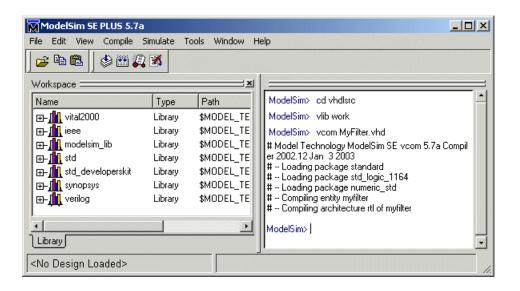

**4** Compile the generated filter and test bench Verilog files. In ModelSim, you compile Verilog code with the vlog command. The following ModelSim commands compile the filter and filter test bench Verilog code.

```

vlog optfir.vhd

vlog optfir_tb.vhd

```

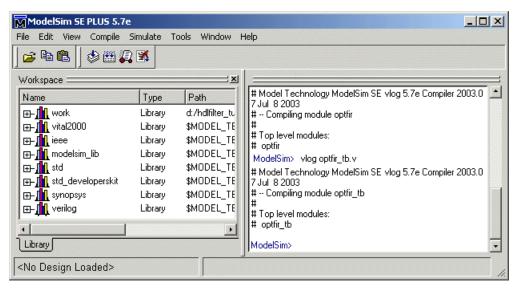

The following screen display shows this command sequence and informational messages displayed during compilation.

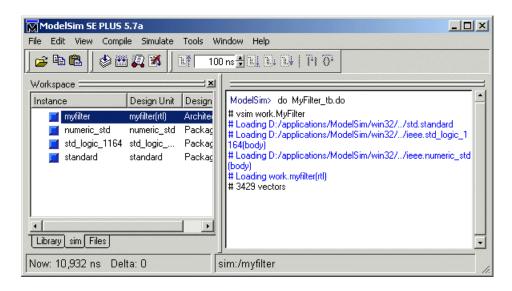

**5** Load the test bench for simulation. The procedure for doing this varies depending on the simulator you are using. In ModelSim, you load the test bench for simulation with the vsim command. For example:

```

vsim optfir_tb

```

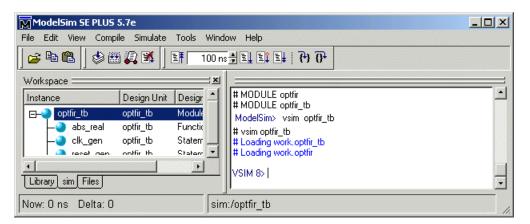

The following ModelSim display shows the results of loading optfir\_tb with the vsim command.

**6** Open a display window for monitoring the simulation as the test bench runs. For example, in ModelSim, you can use the following command to open a **wave** window to view the results of the simulation as HDL waveforms:

add wave \*

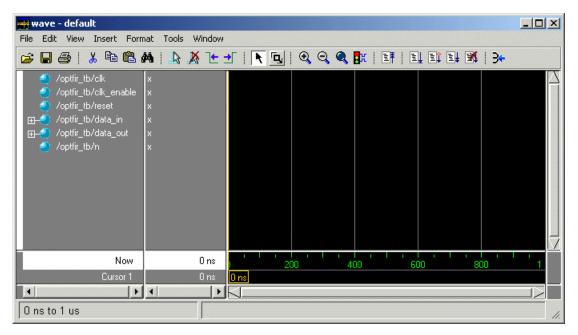

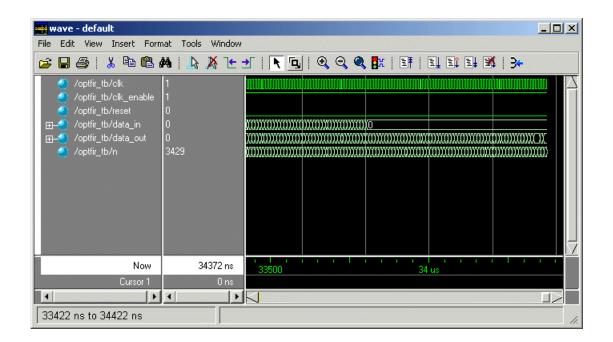

The following Wave window displays:

7 To start running the simulation, issue the appropriate command for your simulator. For example, in ModelSim, you can start a simulation with the run command.

The following ModelSim display shows the run -all command being used to start a simulation.

As your test bench simulation runs, watch for error messages. If any error messages appear, you must interpret them as they pertain to your filter design and the HDL customizations you applied with the Filter Design HDL Coder. You must determine whether the results are expected based on the customizations you specified when generating the filter Verilog code.

The following Wave window shows the simulation results as HDL waveforms.

#### **IIR Filter Tutorial**

This section guides you through the steps for designing a basic quantized discrete-time IIR filter, generating VHDL code for the filter, and verifying the VHDL code with a generated test bench. The procedure is presented in the following topics:

- "Designing an IIR Filter" on page 2-43

- "Quantizing the IIR Filter" on page 2-45

- "Configuring and Generating the IIR Filter's VHDL Code" on page 2-49

- $\bullet\,$  "Getting Familiar with the IIR Filter's Generated VHDL Code" on page 2-55

- "Verifying the IIR Filter's Generated VHDL Code" on page 2-56

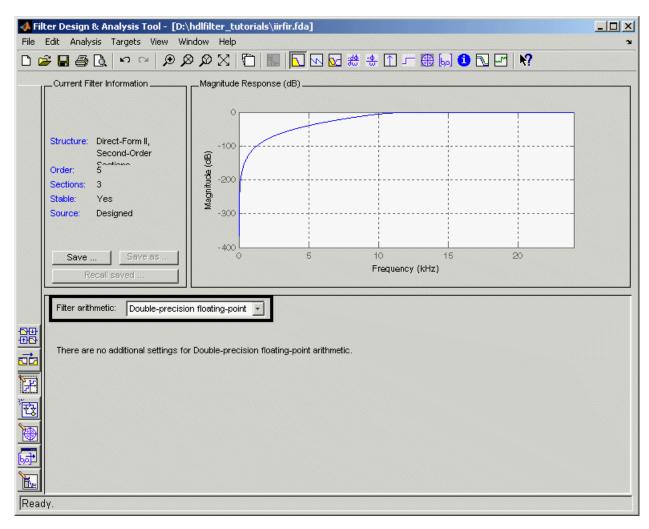

### **Designing an IIR Filter**

One way of designing a filter in the MATLAB environment is to use the FDATool. This section guides you through the procedure of designing and creating a filter for an IIR filter. These instructions assume you are familiar with the MATLAB user interface and the FDATool.

- 1 Start MATLAB.

- **2** Set your MATLAB current directory to the directory you created in "Creating a Directory for Your Tutorial Files" on page 2-2.

- 3 Start the FDATool by entering the fdatool command in the MATLAB Command Window. MATLAB displays the Filter Design & Analysis Tool dialog.

4 In the Filter Design & Analysis Tool dialog, set the following filter options:

| Option        | Value           |

|---------------|-----------------|

| Response Type | Highpass        |

| Design Method | IIR Butterworth |

| Option                   | Value     |

|--------------------------|-----------|

| Filter Order             | 5         |

| Frequency Specifications | Units: Hz |

|                          | Fs: 48000 |

|                          | Fc: 10800 |

**5** Click **Design Filter**. The FDATool creates a filter for the specified design. The following message appears in the FDATool status bar when the task is complete.

Designing Filter... Done

For more information on designing filters with the FDATool, see the FDATool and Filter Design Toolbox documentation.

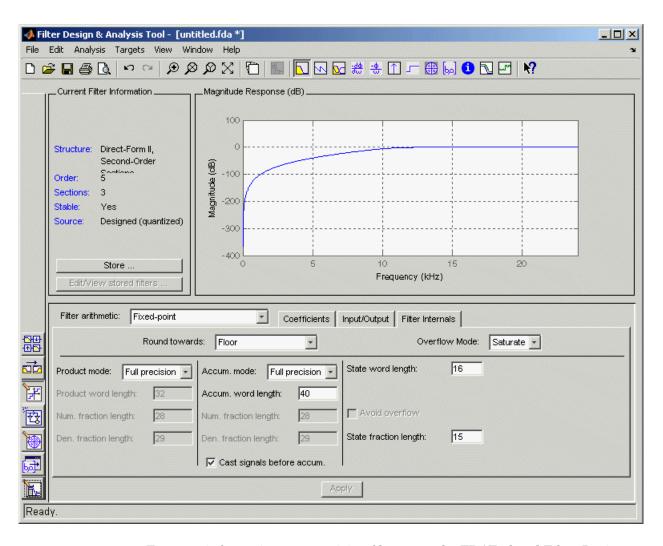

## **Quantizing the IIR Filter**

You should quantize filters for HDL code generation. To quantize your filter,

- 1 Open the IIR filter design you created in "Designing an IIR Filter" on page 2-43 if it is not already open.

- 2 Click the **Set quantization parameters** icon in the left-side tool bar. The FDATool displays the **Filter arithmetic** menu in the bottom half of its dialog.

3 Select Fixed-point from the menu. The FDATool displays the first of three tabbed panels of its dialog.

You use the quantization options to test the effects of various settings with a goal of optimizing the quantized filter's performance and accuracy.

- 4 Click the **Filter Internals** tab and set **Round towards** to Floor and **Overflow Mode** to Saturate.

- **5** Click **Apply**. The quantized filter appears as follows.

For more information on quantizing filters, see the FDATool and Filter Design Toolbox documentation.

## Configuring and Generating the IIR Filter's VHDL Code

After you quantize your filter, you are ready to use the Filter Design HDL Coder to configure and generate the filter's VHDL code. This section guides you through the procedure for starting the Filter Design HDL Coder GUI, setting some options, and generating the VHDL code and a test bench for the IIR filter you designed and quantized in "Designing an IIR Filter" on page 2-43 and "Quantizing the IIR Filter" on page 2-45

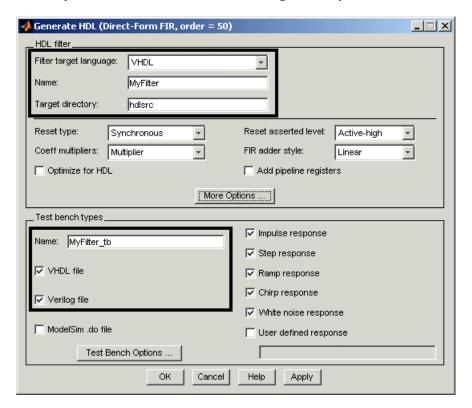

1 Start the Filter Design HDL Coder by clicking Targets->Generate HDL in the FDATool dialog. The FDATool displays the Filter Design HDL Coder dialog.

**2** In the **Name** text box of the **HDL filter** pane, type iir. This option names the VHDL entity and the file that is to contain the filter's VHDL code.

- **3** In the **Name** text box of the **Test bench types** pane, type iir tb. This option names the generated test bench file.

- 4 Click More Options. The Filter Design HDL Coder displays an HDL Options dialog.

- 5 In the Comment in header text box, type Tutorial IIR Filter and then click Apply. The Filter Design HDL Coder adds the comment to the end of the header comment block in each generated file.

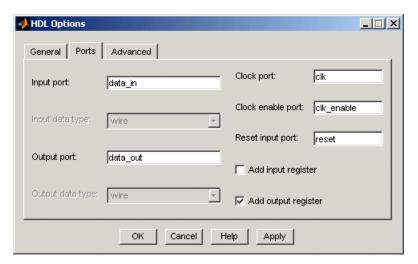

- **6** Click the **Ports** tab. The **Ports** pane appears.

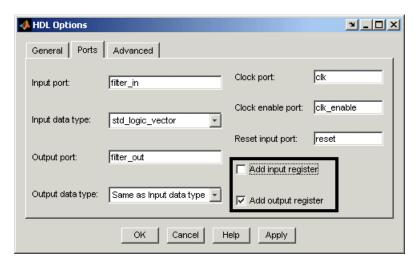

**7** Clear the check box for the **Add output register** option. The **Ports** tab should now look like the following.

- 8 Click Apply.

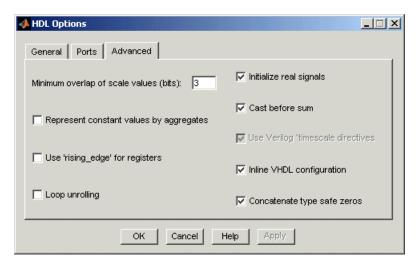

- $\boldsymbol{9}$  Click the  $\boldsymbol{Advanced}$  tab. The  $\boldsymbol{Advanced}$  pane appears.

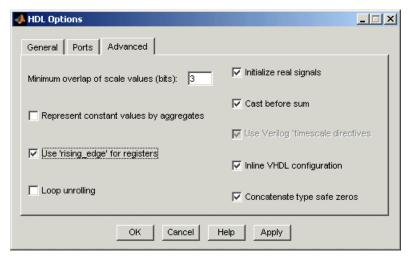

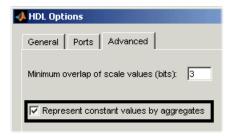

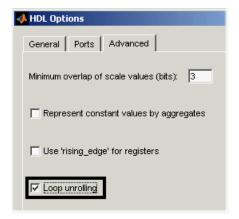

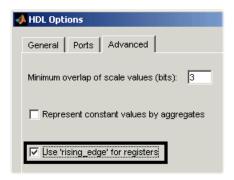

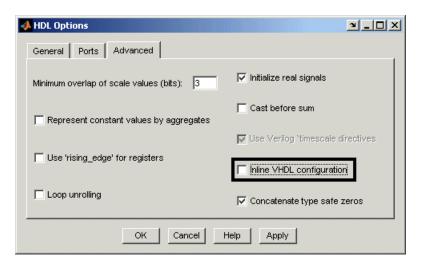

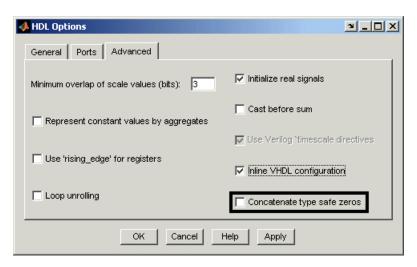

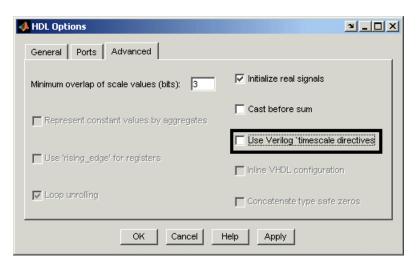

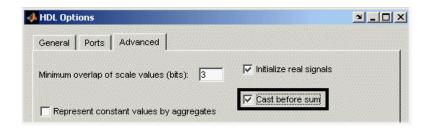

10 Select the **Use 'rising\_edge' for registers** option. The **Advanced** pane should now look like the following.

- 11 Click **Apply** to register your changes and then **OK** to close the dialog.

- 12 Click **Test Bench Options**. The Filter Design HDL Coder displays a **Test Bench Options** dialog.

You use this dialog to customize the generated test bench.

- **13** For this tutorial, apply the default settings by clicking **OK**.

- **14** In the **Generate HDL** dialog, click **Apply** or **OK** to start the code generation process. **OK** closes the dialog.

The Filter Design HDL Coder displays the following messages in the MATLAB Command Window as it generates the filter and test bench VHDL files:

```

### Starting VHDL code generation process for filter: iir

### Generating iir.vhd file in: hdlsrc

### Starting generation of iir VHDL entity

### Starting generation of iir VHDL architecture

### Second-order section, # 1

### Second-order section, # 2

### First-order section, # 3

### Successful completion of VHDL code generation process for

filter: iir

### Starting generation of VHDL Test Bench

### Generating input stimulus

```

```

### Done generating input stimulus; length 2172 samples.

### Generating VHDL file iir_tb.vhd in: hdlsrc

### Done generating VHDL test bench.

```

As the messages indicate, the Filter Design HDL Coder creates the directory hdlsrc under your current working directory and places the files iir.vhd and iir\_tb.vhd in that directory.

The generated VHDL code has the following characteristics:

- VHDL entity named iir.

- Registers that use asynchronous resets when the reset signal is active high (1).

- Ports have the following default names:

| VHDL Port          | Name       |

|--------------------|------------|

| Input              | filter_in  |

| Output             | filter_out |

| Clock input        | clk        |

| Clock enable input | clk_enable |

| Reset input        | reset      |

- An extra register for handling filter input.

- Clock input, clock enable input and reset ports are of type STD\_LOGIC and data input and output ports are of typeSTD\_LOGIC VECTOR.

- Coefficients are named coeff*n*, where *n* is the coefficient number, starting with 1.

- Type safe representation is used when zeros are concatenated: '0' & '0'...

- Registers are generated with the rising\_edge function rather than the statement ELSIF clk'event AND clk='1' THEN.

- The postfix string process is appended to process names.

The generated test bench:

• Is a portable VHDL file.

- Forces clock, clock enable, and reset input signals.

- Forces the clock enable input signal to active high.

- Drives the clock input signal high (1) for 5 nanoseconds and low (0) for 5 nanoseconds.

- Forces the reset signal for two cycles plus a hold time of 2 nanoseconds.

- Applies a hold time of 2 nanoseconds to data input signals.

- Applies step, ramp, and chirp stimulus types.

# Getting Familiar with the IIR Filter's Generated VHDL Code

Get familiar with the filter's generated VHDL code by opening and browsing through the file iir.vhd in an ASCII or HDL simulator editor.

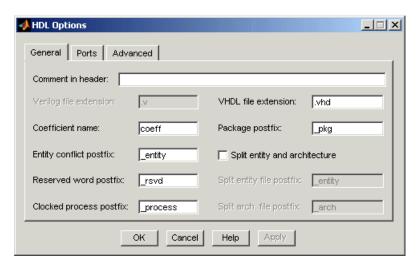

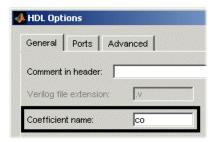

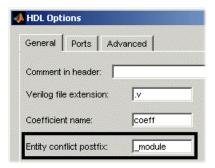

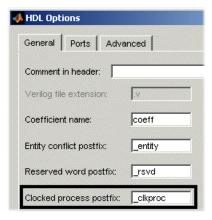

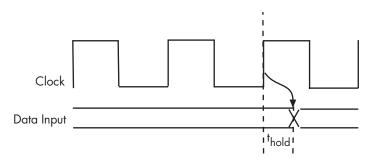

- 1 Open the generated VHDL filter file iir.vhd.